# TLE84110EL

Deca-Half-Bridge Driver IC

**Automotive Power**

### **Table of Contents**

# **Table of Contents**

| 1                                                                                                                      | Overview                                                                                                                                                                                                                                                                                                                                                                              | 3                                                        |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2                                                                                                                      | Block Diagram                                                                                                                                                                                                                                                                                                                                                                         | 4                                                        |

| <b>3</b><br>3.1<br>3.2                                                                                                 | Pin Configuration         Pin Assignment         Pin Definitions and Functions                                                                                                                                                                                                                                                                                                        | 6                                                        |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.4                                                                                   | General Product Characteristics Absolute Maximum Ratings Functional Range Thermal Resistance Electrical Characteristics                                                                                                                                                                                                                                                               | 8<br>9<br>10                                             |

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.4.1<br>5.2.4.2<br>5.2.5<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3 | Block Description         General         Power Supply         General         Sleep Mode         Reverse Polarity Protection         Power Supply Monitoring $V_S$ Undervoltage $V_S$ Overvoltage         Reset Behavior         Temperature Monitoring         Protection and Diagnosis         Short Circuit of Output to Supply or Ground         Open Load         Cross-Current | 15<br>15<br>15<br>15<br>15<br>16<br>16<br>17<br>18<br>18 |

| 6<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2                                                                               | SPI General Status Register Reset SPI Bit Definitions Control - Word Diagnosis - Word                                                                                                                                                                                                                                                                                                 | 21<br>23<br>24<br>24                                     |

| <b>7</b><br>7.1<br>7.2                                                                                                 | Application Information         Application Diagram         Thermal application information                                                                                                                                                                                                                                                                                           | 28                                                       |

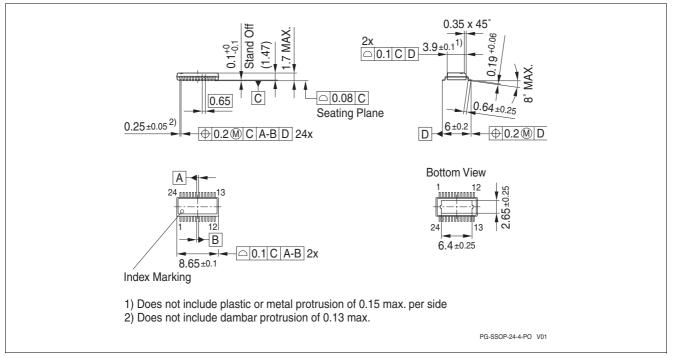

| 8                                                                                                                      | Package Outlines                                                                                                                                                                                                                                                                                                                                                                      | 31                                                       |

| 9                                                                                                                      | Revision History                                                                                                                                                                                                                                                                                                                                                                      | 32                                                       |

# **Deca-Half-Bridge Driver IC**

**TLE84110EL**

#### 1 Overview

#### **Features**

- 10 Half Bridge Power Outputs

- 3.3V / 5V compatible inputs with hysteresis

- · Independently Diagnosable Outputs

- 16-bit Standard SPI interface with daisy chain capability for control and diagnosis

- Open load diagnostics in ON-state for all outputs

- All outputs with overload and short circuit protection and diagnosis

- · Overtemperature prewarning and protection

- · Over- and Undervoltage lockout

- Cross-current protection

- Thermally enhanced exposed pad package

- Green Product (RoHS compliant)

- AEC Qualified

PG-SSOP-24-4

#### **Description**

The TLE84110EL is a protected Deca-Half-Bridge-Driver designed especially for automotive motion control applications such as Heating, Ventilation and Air Conditioning (HVAC) flap DC motor control. It is part of the MonolythIC family in Infineon's Smart Power Technology SPT® which combines bipolar and CMOS control circuitry with DMOS power devices.

The 10 half bridge drivers are designed to drive DC motor loads in sequential or parallel operation. Operation modes forward (cw), reverse (ccw), brake and high impedance are controlled from a 16-bit SPI interface. The diagnosis features such as short circuit, open load, power supply failure and overtemperature in combination with its low quiescent current makes this device attractive for automotive applications. The extremely small fine pitch exposed pad PG-SSOP-24-4 package in a SO -14 body provides good thermal performance and reduces PCB-board space and costs.

#### Table 1 Product Summary

| Operating Voltage                                                                    | $V_{S}$                          | 7 18 V    |

|--------------------------------------------------------------------------------------|----------------------------------|-----------|

| Logic Supply Voltage                                                                 | $V_{DD}$                         | 3.0 5.5 V |

| Maximum Supply Voltage for Load Dump Protection                                      | $V_{S(LD)}$                      | 40 V      |

| Minimum Overcurrent Threshold                                                        | $I_{\mathrm{SD1-10\_MOTOR}}$     | 0.8 A     |

| $\overline{\text{Maximum On-State Path Resistance at } T_{j} = 150^{\circ}\text{C}}$ | R <sub>DSON(total)_HSx+LSy</sub> | 2 + 2 Ω   |

| Typical Quiescent Current at $T_j$ = 85°C                                            | I <sub>S (off))</sub>            | 1 μΑ      |

| Maximum SPI Access Frequency                                                         | $f_{\sf SCLK}$                   | 5 MHz     |

| Туре       | Package      | Marking    |

|------------|--------------|------------|

| TLE84110EL | PG-SSOP-24-4 | TLE84110EL |

Data Sheet 3 Rev. 1.0, 2010-04-27

**Block Diagram**

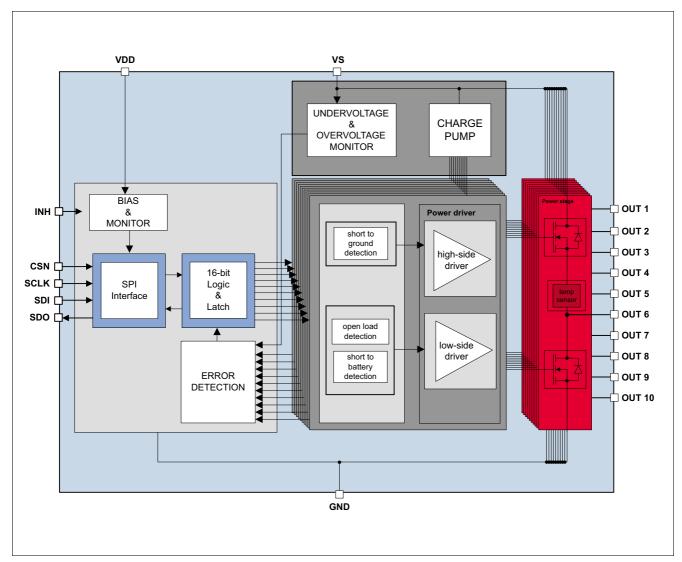

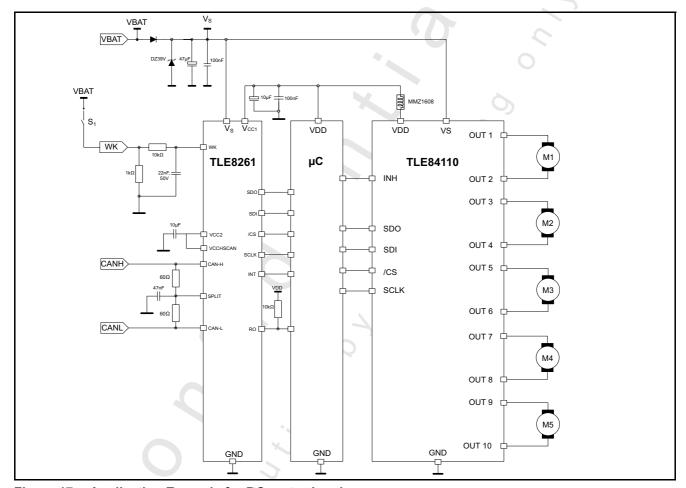

# 2 Block Diagram

Figure 1 Block Diagram

**Block Diagram**

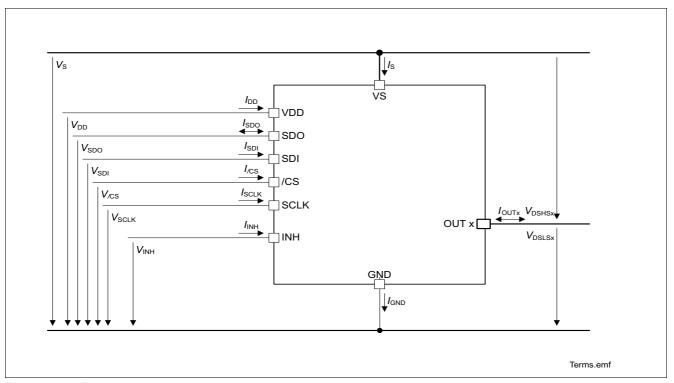

Figure 2 Terms

**Pin Configuration**

# **3** Pin Configuration

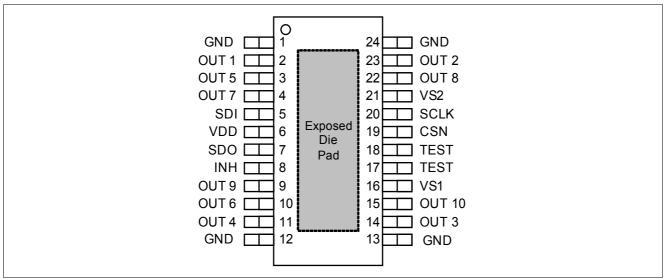

# 3.1 Pin Assignment

Figure 3 Pin Configuration

**Pin Configuration**

### 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                                                         |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND    | Ground                                                                                                                           |

| 2   | OUT 1  | Power Half-Bridge 1                                                                                                              |

| 3   | OUT 5  | Power Half-Bridge 5                                                                                                              |

| 4   | OUT 7  | Power Half-Bridge 7                                                                                                              |

| 5   | SDI    | Serial-Data-Input                                                                                                                |

| 6   | VDD    | Logic Supply Voltage                                                                                                             |

| 7   | SDO    | Serial-Data-Output                                                                                                               |

| 8   | INH    | Inhibit input with internal pull-down; Place device in standby mode by pulling the INH line LOW                                  |

| 9   | OUT 9  | Power Half-Bridge 9                                                                                                              |

| 10  | OUT 6  | Power Half-Bridge 6                                                                                                              |

| 11  | OUT 4  | Power Half-Bridge 4                                                                                                              |

| 12  | GND    | Ground                                                                                                                           |

| 13  | GND    | Ground                                                                                                                           |

| 14  | OUT 3  | Power Half-Bridge 3                                                                                                              |

| 15  | OUT 10 | Power Half-Bridge 10                                                                                                             |

| 16  | VS1    | Power Supply Voltage for Group 1 supplying current to OUT 3, OUT 4, OUT 6, OUT 9 and OUT 10.                                     |

| 17  | TEST   | Test input with internal pull down. Used for production test only. This pin should be left open or connected to ground on board. |

| 18  | TEST   | Test input with internal pull down. Used for production test only. This pin should be left open or connected to ground on board. |

| 19  | CSN    | Chip-Select-Not-Input                                                                                                            |

| 20  | SCLK   | Serial Clock Input                                                                                                               |

| 21  | VS2    | Power Supply Voltage for Group 2 supplying current to OUT 1, OUT 2, OUT 5, OUT 7 and OUT 8.                                      |

| 22  | OUT 8  | Power Half-Bridge 8                                                                                                              |

| 23  | OUT 2  | Power Half-Bridge 2                                                                                                              |

| 24  | GND    | Ground                                                                                                                           |

| EDP | -      | Exposed Die Pad; For cooling purposes only; Do not use as electrical ground.1)                                                   |

|     |        |                                                                                                                                  |

<sup>1)</sup> The exposed die pad at the bottom of the package allows better heat dissipation from the device via the PCB. The exposed die pad is not connected to any active part of the IC. When connecting onto PCB, it can either be left floating or connected to GND for the best EMC and thermal performance.

Note: All GND pins must be externally connected together to a common GND potential. All VS pins must be externally connected together to a common Vs potential. See **Figure 17** for more Application Information.

### 4 General Product Characteristics

# 4.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings 1)

$T_i$  = -40 °C to +150 °C

| Pos.    | Parameter                                     | Symbol                                                                               | Limit Values |      | Unit | Conditions                                                                                  |  |

|---------|-----------------------------------------------|--------------------------------------------------------------------------------------|--------------|------|------|---------------------------------------------------------------------------------------------|--|

|         |                                               |                                                                                      | Min. Max.    |      |      |                                                                                             |  |

| Voltage | s                                             |                                                                                      |              |      |      |                                                                                             |  |

| 4.1.1   | Supply voltage                                | $V_{S}$                                                                              | -0.3         | 40   | V    | $V_{\rm S} = V_{\rm S1} = V_{\rm S2}$                                                       |  |

| 4.1.2   | Logic supply voltage                          | $V_{DD}$                                                                             | -0.3         | 5.5  | V    | 0 V < V <sub>S</sub> < 40 V                                                                 |  |

| 4.1.3   | Logic input voltages<br>(SDI, SCLK, CSN; INH) | $\begin{matrix} V_{\rm SDI}, V_{\rm SCLK}, \\ V_{\rm CSN}, V_{\rm INH} \end{matrix}$ | -0.3         | 5.5  | V    | $0 \text{ V} < V_{\text{S}} < 40 \text{ V}$<br>$0 \text{ V} < V_{\text{DD}} < 5.5 \text{V}$ |  |

| 4.1.4   | Logic output voltage (SDO)                    | $V_{SDO}$                                                                            | -0.3         | 5.5  | V    | 0 V < V <sub>S</sub> < 40 V<br>0 V < V <sub>DD</sub> < 5.5V                                 |  |

| Current | s                                             |                                                                                      |              |      |      |                                                                                             |  |

| 4.1.5   | Continuous Supply Current for $V_{\rm S1}$    | $I_{\mathrm{S1}}$                                                                    | 0            | 2.50 | Α    | _                                                                                           |  |

| 4.1.6   | Continuous Supply Current for $V_{\rm S2}$    | $I_{\mathrm{S2}}$                                                                    | 0            | 2.50 | Α    | _                                                                                           |  |

| Temper  | atures                                        |                                                                                      |              |      |      |                                                                                             |  |

| 4.1.7   | Junction temperature                          | $T_{\rm j}$                                                                          | -40          | 150  | °C   | _                                                                                           |  |

| 4.1.8   | Storage temperature                           | $T_{\mathrm{stg}}$                                                                   | -50          | 150  | °C   | _                                                                                           |  |

| ESD Su  | sceptibility                                  |                                                                                      | •            |      |      |                                                                                             |  |

| 4.1.9   | ESD capability of OUTx and $V_{S}$ pin        | $V_{ESD}$                                                                            | -4           | 4    | kV   | 2)                                                                                          |  |

| 4.1.10  | ESD capability of other pins                  | $V_{ESD}$                                                                            | -2           | 2    | kV   | 2)                                                                                          |  |

|         |                                               |                                                                                      |              |      |      | 1                                                                                           |  |

<sup>1)</sup> Not subject to production test, specified by design.

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

Data Sheet 8 Rev. 1.0, 2010-04-27

<sup>2)</sup> Human Body Model according to ANSI EOS\ESD S5.1 standard (eqv. to MIL STD 883D and JEDEC JESD22-A114)

# 4.2 Functional Range

| Pos.  | Parameter                                       | Symbol                                         | Lim                 | it Values           | Unit | Conditions                                                                      |

|-------|-------------------------------------------------|------------------------------------------------|---------------------|---------------------|------|---------------------------------------------------------------------------------|

|       |                                                 |                                                | Min.                | Max.                |      |                                                                                 |

| 4.2.1 | Supply voltage range for normal operation       | $V_{S(nor)}$                                   | 7                   | 18                  | V    | _                                                                               |

| 4.2.2 | Extended Supply Voltage Range for Operation     | $V_{S(ext)}$                                   | V <sub>UV OFF</sub> | V <sub>OV OFF</sub> | V    | Limit Values Deviations Possible; After $V_{\rm S}$ rising above $V_{\rm UVON}$ |

| 4.2.3 | Supply Voltage Slew Rate                        | $ dV_s/dt $                                    | -                   | 10                  | V/µs | $V_{\rm S}$ increasing and decreasing <sup>1)</sup>                             |

| 4.2.4 | Logic supply voltage range for normal operation | $V_{DD}$                                       | 3.0                 | 5.5                 | V    | _                                                                               |

| 4.2.5 | Logic input voltages (DI, CLK, CSN; INH)        | $V_{ m DI},V_{ m CLK},\ V_{ m CSN},V_{ m INH}$ | -0.3                | 5.5                 | V    | _                                                                               |

| 4.2.6 | Junction temperature                            | $T_{j}$                                        | -40                 | 150                 | °C   | _                                                                               |

<sup>1)</sup> Not subject to production test, specified by design.

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

Data Sheet 9 Rev. 1.0, 2010-04-27

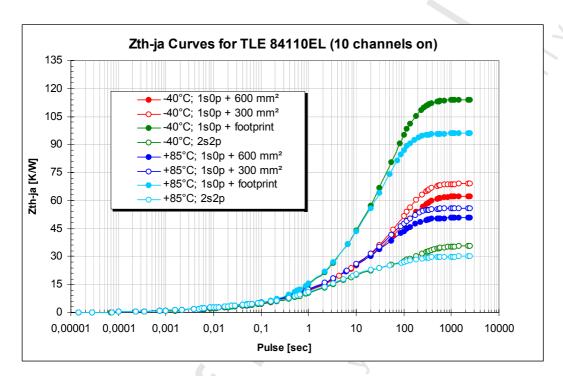

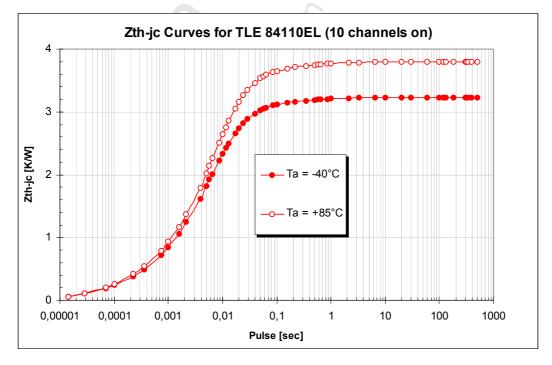

#### 4.3 Thermal Resistance

| Pos.   | Parameter                                                 | Symbol                         |      | Limit Val | ues  | Unit | Conditions |

|--------|-----------------------------------------------------------|--------------------------------|------|-----------|------|------|------------|

|        |                                                           |                                | Min. | Тур.      | Max. |      |            |

| 4.3.1  | Junction to Case, Ta = -40°C                              | $R_{ m thjC\_cold}$            | _    | 3         | _    | K/W  | 1)         |

| 4.3.2  | Junction to Case, Ta = 85°C                               | $R_{thjC\_hot}$                | _    | 4         | _    | K/W  | 1)         |

| 4.3.3  | Junction to Ambient, Ta = -40°C (1s0p, minimal footprint) | $R_{ m thjA\_cold\_min}$       | _    | 114       | _    | K/W  | 1) 2)      |

| 4.3.4  | Junction to Ambient, Ta = 85°C (1s0p, minimal footprint)  | $R_{ m thjA\_hot\_min}$        | _    | 96        | _    | K/W  | 1) 2)      |

| 4.3.5  | Junction to Ambient, Ta = -40°C (1s0p, 300mm2 Cu)         | $R_{ m thjA\_cold\_300}$       | -    | 69        | _    | K/W  | 1) 3)      |

| 4.3.6  | Junction to Ambient, Ta = 85°C (1s0p, 300mm2 Cu)          | $R_{\rm thjA\_hot\_300}$       | -    | 56        | -    | K/W  | 1) 3)      |

| 4.3.7  | Junction to Ambient, Ta = -40°C (1s0p, 600mm2 Cu)         | $R_{\mathrm{thjA\_cold\_600}}$ | -    | 62        | -    | K/W  | 1) 4)      |

| 4.3.8  | Junction to Ambient, Ta = 85°C (1s0p, 600mm2 Cu)          | $R_{ m thjA\_hot\_600}$        | _    | 50        | _    | K/W  | 1) 4)      |

| 4.3.9  | Junction to Ambient, Ta = -40°C (2s2p)                    | $R_{ m thjA\_cold\_2s2p}$      | _    | 35        | _    | K/W  | 1) 5)      |

| 4.3.10 | Junction to Ambient, Ta = 85°C (2s2p)                     | $R_{ m thjA\_hot\_2s2p}$       | _    | 30        | _    | K/W  | 1) 5)      |

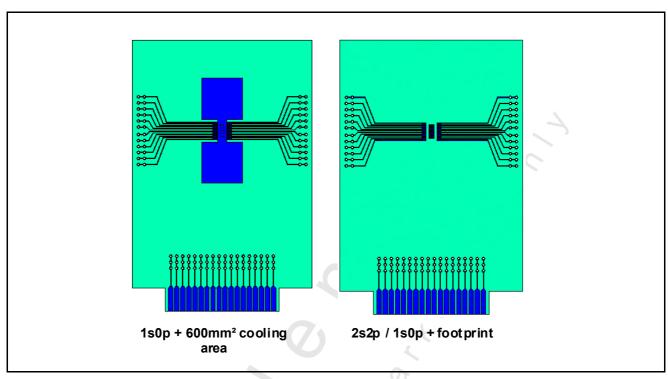

- 1) Not subject to production test, specified by design.

- 2) Specified RthJA value is according to JEDEC JESD51-2,-3 at natural convection on FR4 1s0p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with minimal footprint copper area and 35 μm thickness. Ta = -40°C, Ch 1 to Ch 10 are dissipating a total of 1.8W (0.18W each).

- 3) Specified RthJA value is according to JEDEC JESD51-2,-3 at natural convection on FR4 1s0p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with additional cooling of 300 mm2 copper area and 35 µm thickness. Ta = -40°C, Ch 1 to Ch 10 are dissipating a total of 2.5W (0.25W each). Ta = 85°C, Ch 1 to Ch 10 are dissipating a total of 1.8W (0.18W each).

- 4) Specified RthJA value is according to JEDEC JESD51-2,-3 at natural convection on FR4 1s0p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with additional cooling of 600 mm2 copper area and 35 μm thickness. Ta = -40°C, Ch 1 to Ch 10 are dissipating a total of 2.5W (0.25W each). Ta = 85°C, Ch 1 to Ch 10 are dissipating a total of 1.8W (0.18W each).

- 5) Specified RthJA value is according to JEDEC JESD51-2,-3 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (4 x 35μm Cu). Ta = -40°C, Ch 1 to Ch 10 are dissipating a total of 2.5W (0.25W each). Ta = 85°C, Ch 1 to Ch 10 are dissipating a total of 1.8W (0.18W each).

Data Sheet 10 Rev. 1.0, 2010-04-27

### 4.4 Electrical Characteristics

#### **Electrical Characteristics**

$V_{\rm S}$ = 7 V to 18 V,  $V_{\rm DD}$ = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40 °C to +150 °C, INH = HIGH;  $I_{\rm OUT1-10}$  = 0 A; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.     | Parameter                            | Symbol                        | L    | imit Val | ues  | Unit | Conditions                                                        |

|----------|--------------------------------------|-------------------------------|------|----------|------|------|-------------------------------------------------------------------|

|          |                                      |                               | Min. | Тур.     | Max. |      |                                                                   |

| Curren   | t Consumption, INH = GND             | 1                             | II.  |          |      |      |                                                                   |

| 4.4.1    | Supply Quiescent current             | $I_{SQ}$                      | _    | 1        | 2.5  | μА   | $V_{\rm S}$ = 13.5 V;<br>$V_{\rm DD}$ = 0 V<br>$T_{\rm j}$ = 85°C |

| 4.4.2    | Logic supply quiescent current       | $I_{DD_{Q}}$                  | _    | 0.5      | 1    | μA   | $T_{\rm i} = 85^{\circ}{\rm C}$                                   |

| 4.4.3    | Total quiescent current              | $I_{SQ} + I_{DD_Q}$           | _    | 2        | 4    | μA   | $T_{\rm i} = 85^{\circ}{\rm C}$                                   |

| Curren   | t Consumption, INH = HIGH            |                               | II.  |          |      |      |                                                                   |

| 4.4.4    | Supply current                       | $I_{S}$                       | -    | 4.5      | 10   | mA   | Power drivers and power stages are of                             |

| 4.4.5    | Logic supply current                 | $I_{DD}$                      | _    | 1.5      | 3    | mA   | SPI not active                                                    |

| 4.4.6    | Logic supply current                 | $I_{\mathrm{DD\_RUN}}$        | _    | 5        | _    | mA   | $V_{\rm DD}$ = 3.0V;<br>SPI 5MHz                                  |

| 4.4.7    | Total supply current                 | $I_{\rm S} + I_{\rm DD\_RUN}$ | _    | 9.5      | _    | mA   | _                                                                 |

| Over- a  | nd Undervoltage Lockout              |                               |      |          | -    |      | •                                                                 |

| 4.4.8    | UV Switch ON voltage                 | $V_{UVON}$                    | _    | _        | 5.2  | V    | $V_{\rm S}$ increasing                                            |

| 4.4.9    | UV Switch OFF voltage                | $V_{UVOFF}$                   | 4    | _        | 5.0  | V    | $V_{\rm S}$ decreasing                                            |

| 4.4.10   | UV ON/OFF hysteresis                 | $V_{UVHY}$                    | _    | 0.25     | _    | V    | V <sub>UV ON</sub> - V <sub>UV OFF</sub>                          |

| 4.4.11   | OV Switch OFF voltage                | $V_{OVOFF}$                   | 21   | _        | 25   | V    | $V_{\rm S}$ increasing;                                           |

| 4.4.12   | OV Switch ON voltage                 | $V_{OVON}$                    | 20   | _        | 24   | V    | $V_{\rm S}$ decreasing;                                           |

| 4.4.13   | OV ON/OFF hysteresis                 | $V_{OVHY}$                    | _    | 1        | _    | V    | $V_{\text{OV OFF}}$ - $V_{\text{OV ON}}$ ;                        |

| 4.4.14   | V <sub>DD</sub> Power-On-Reset       | $V_{DD\;POR}$                 | 2.60 | 2.80     | 3.00 | V    | $V_{\mathrm{DD}}$ increasing                                      |

| 4.4.15   | V <sub>DD</sub> Power-Off-Reset      | $V_{ m DD~POffR}$             | 2.50 | 2.70     | 2.90 | V    | $V_{\mathrm{DD}}$ decreasing                                      |

| Static [ | Drain-source ON-Resistance           |                               |      |          | ·    |      |                                                                   |

| 4.4.16   | High- and Low-side switch            | R <sub>DSON(1-10)</sub>       | _    | 0.8      | _    | Ω    | $I_{OUT (1-10)}$ = ±0.5 A;<br>$T_{j}$ = 25 °C                     |

|          |                                      |                               | _    | 1.4      | 2    | Ω    | $I_{OUT (1-10)}$ = ±0.5 A;<br>$T_{j}$ = 150 °C                    |

| Output   | Protection and Diagnosis             |                               |      |          |      |      |                                                                   |

| High-Si  | ide Switches                         |                               |      |          |      |      |                                                                   |

| 4.4.17   | HS Overcurrent Shutdown<br>Threshold | $I_{SD\_HS}$                  | -1.6 | -1.15    | -0.8 | A    | HS Switch; $V_{\rm S}$ =13.5V; See Figure 7                       |

| 4.4.18   | HS Short Circuit Current Limit       | $I_{SC\_HS}$                  | -2.0 | -1.5     | -1.0 | Α    | 1)                                                                |

| 4.4.19   | HS_Shutdown Delay Time               | $t_{\sf dSD}$                 | 10   | 25       | 50   | μs   | HS Switch; $V_{\rm S}$ =13.5V; See Figure 7                       |

Data Sheet 11 Rev. 1.0, 2010-04-27

### Electrical Characteristics (cont'd)

$V_{\rm S}$ = 7 V to 18 V,  $V_{\rm DD}$ = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40 °C to +150 °C, INH = HIGH;  $I_{\rm OUT1-10}$  = 0 A; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.     | Parameter                                 | Symbol            | L    | imit Val | ues  | Unit            | Conditions                                  |

|----------|-------------------------------------------|-------------------|------|----------|------|-----------------|---------------------------------------------|

|          |                                           |                   | Min. | Тур.     | Max. |                 |                                             |

| Low-Sid  | de Switches                               | •                 | ı    | 1        |      | •               |                                             |

| 4.4.20   | LS Overcurrent Shutdown<br>Threshold      | $I_{SD\_LS}$      | 8.0  | 1.15     | 1.6  | A               | LS Switch; $V_{\rm S}$ =13.5V; See Figure 7 |

| 4.4.21   | LS Short Circuit Current Limit            | $I_{SC\_LS}$      | 1.0  | 1.5      | 2.0  | А               | 1)                                          |

| 4.4.22   | LS_Shutdown Delay Time                    | $t_{\sf dSD}$     | 10   | 25       | 50   | μs              | LS Switch; $V_{\rm S}$ =13.5V; See Figure 7 |

| 4.4.23   | Open Load Detection Current               | $I_{OLD}$         | 3    | 8        | 15   | mA              | LS Switch;                                  |

| 4.4.24   | Open Load Delay Time                      | $t_{\sf dOLD}$    | 200  | 350      | 600  | μs              | $V_{\rm S}$ =13.5V; See Figure 8            |

| Output   | Switching Times                           |                   |      |          |      |                 |                                             |

| 4.4.25   | High-Side ON delay-time                   | $t_{\sf dONH}$    | _    | 7.5      | 12   | μs              | $V_{\rm S}$ =13.5V, resistive               |

| 4.4.26   | High-Side OFF delay-time                  | $t_{dOFFH}$       | _    | 3        | 6    | μs              | Load = $100\Omega$ , See                    |

| 4.4.27   | Low-Side ON delay-time                    | $t_{dONL}$        | _    | 6.5      | 12   | μs              | Figure 9 and Figure 10                      |

| 4.4.28   | Low-Side OFF delay-time                   | $t_{dOFFL}$       | _    | 2        | 5    | μs              | rigule 10                                   |

| 4.4.29   | Dead Time H to L                          | $t_{DHL}$         | 1.5  | _        | _    | μs              |                                             |

| 4.4.30   | Dead Time L to H                          | $t_{DLH}$         | 2.5  | _        | _    | μs              |                                             |

| 4.4.31   | High-Side RiseTime                        | $t_{ONH}$         | _    | 4        | _    | μs              |                                             |

| 4.4.32   | High-Side Fall Time                       | $t_{OFFH}$        | _    | 2        | _    | μs              |                                             |

| 4.4.33   | Low-Side RiseTime                         | $t_{OFFL}$        | _    | 1        | _    | μs              |                                             |

| 4.4.34   | Low-Side Fall Time                        | $t_{ONL}$         | _    | 1        | _    | μs              |                                             |

| Input In | terface, Logic Inputs INH                 |                   |      |          |      |                 |                                             |

| 4.4.35   | High-input voltage                        | $V_{INHH}$        | 70   | _        | _    | $\%~V_{ m DD}$  | _                                           |

| 4.4.36   | Low-input voltage                         | $V_{INHL}$        | _    | _        | 30   | $\%~V_{ m DD}$  | _                                           |

| 4.4.37   | Hysteresis of input voltage               | $V_{INHHY}$       | 50   | 200      | 500  | mV              | _                                           |

| 4.4.38   | Pull down resistor                        | $R_{PD\_INH}$     | _    | 120      | _    | kΩ              | _                                           |

| SPI INT  | TERFACE                                   |                   |      |          | ·    |                 |                                             |

| Delay T  | ime from Sleep mode to first Data i       | n                 |      |          |      |                 |                                             |

| 4.4.39   | Setup time                                | $t_{set}$         | _    | _        | 100  | μs              | 1)                                          |

| 4.4.40   | Time between two consecutive SRR commands | $t_{SRR}$         | 100  | _        | _    | μs              | 1)                                          |

| Input In | terface, Logic Inputs SDI, SCLK, C        | SN                | •    | •        |      | •               |                                             |

| 4.4.41   | High-input voltage                        | $V_{IH}$          | 70   | _        | _    | $\%~V_{DD}$     | _                                           |

| 4.4.42   | Low-input voltage                         | $V_{IL}$          | _    | _        | 30   | $\%~V_{\rm DD}$ | _                                           |

| 4.4.43   | Hysteresis of input voltage               | $V_{IHY}$         | 50   | 200      | 500  | mV              | _                                           |

| 4.4.44   | Pull up resistor at pin CSN               | $R_{\sf PU\_CSN}$ | _    | 140      | _    | kΩ              | _                                           |

| 4.4.45   | Pull down resistor at pin SDI, SCLK       |                   | -    | 120      | -    | kΩ              | _                                           |

Data Sheet 12 Rev. 1.0, 2010-04-27

# Electrical Characteristics (cont'd)

$V_{\rm S}$ = 7 V to 18 V,  $V_{\rm DD}$ = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40 °C to +150 °C, INH = HIGH;  $I_{\rm OUT1-10}$  = 0 A; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.     | Parameter                                    | Symbol               | L                     | imit Val              | ues    | Unit     | Conditions                                                                                                               |  |

|----------|----------------------------------------------|----------------------|-----------------------|-----------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------|--|

|          |                                              |                      | Min.                  | Тур.                  | Max.   |          |                                                                                                                          |  |

| 4.4.46   | Input capacitance at pin CSN, SDI or SCLK    | $C_{I}$              | - 10                  | 10                    | 15     | pF       | $0V < V_{DD} < 5.25V^{1)}$                                                                                               |  |

| Input In | terface, Logic Outputs SDO                   |                      |                       |                       |        |          |                                                                                                                          |  |

| 4.4.47   | High-output voltage                          | $V_{SDOH}$           | V <sub>DD</sub> - 1.0 | V <sub>DD</sub> - 0.7 | _      | V        | $I_{\rm SDOH}$ = -1 mA                                                                                                   |  |

| 4.4.48   | Low-output voltage                           | $V_{SDOL}$           | _                     | 0.2                   | 0.4    | V        | $I_{\mathrm{SDOL}}$ = 1.6 mA                                                                                             |  |

| 4.4.49   | Tri-state Leakage Current                    | $I_{SDOLK}$          | -10                   | _                     | 10     | μΑ       | $\begin{aligned} V_{\mathrm{CSN}} &= V_{\mathrm{DD}} \\ \mathrm{OV} &< V_{\mathrm{SDO}} < V_{\mathrm{DD}} \end{aligned}$ |  |

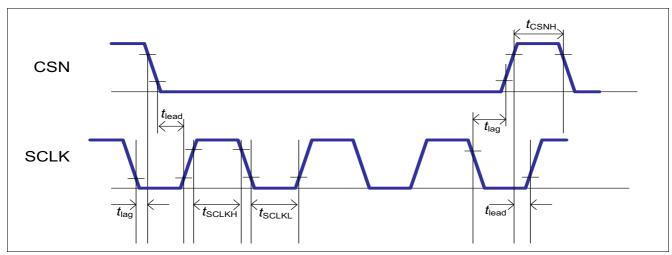

| Data In  | put Timing. See Figure 12 and Figu           | re 15                |                       | -                     | -      |          |                                                                                                                          |  |

| 4.4.50   | SCLK Frequency                               | $f_{CLK}$            | _                     | _                     | 5      | MHz      | 1)                                                                                                                       |  |

| 4.4.51   | SCLK Period                                  | $t_{pCLK}$           | 500<br>200            | _<br>_                | _<br>_ | ns<br>ns | $V_{\rm DD}$ = 5.25V $V_{\rm DD}$ = 3.0V <sup>1)</sup>                                                                   |  |

| 4.4.52   | SCLK High Time                               | $t_{SCLKH}$          | 85                    | _                     | _      | ns       | 1)                                                                                                                       |  |

| 4.4.53   | SCLK Low Time                                | $t_{SCLKL}$          | 85                    | _                     | _      | ns       | 1)                                                                                                                       |  |

| 4.4.54   | SCLK Setup Time                              | $t_{\text{lag}}$     | 85                    | _                     | _      | ns       | 1)                                                                                                                       |  |

| 4.4.55   | SDI Setup Time                               | $t_{\rm SDI\_setup}$ | 50                    | _                     | _      | ns       | 1)                                                                                                                       |  |

| 4.4.56   | SDI Hold Time                                | $t_{\rm SDI\_hold}$  | 50                    | _                     | _      | ns       | 1)                                                                                                                       |  |

| 4.4.57   | CSN Setup Time                               | $t_{lead}$           | 100                   | _                     | _      | ns       | 1)                                                                                                                       |  |

| 4.4.58   | CSN High Time                                | $t_{CSNH}$           | 500                   | _                     | _      | ns       | 1) 2)                                                                                                                    |  |

| 4.4.59   | Input Signal Rise Time at pin SDI, SCLK, CSN | $t_{\sf rIN}$        | _                     | _                     | 50     | ns       | 1)                                                                                                                       |  |

| 4.4.60   | Input Signal Fall Time at pin SDI, SCLK, CSN | $t_{fIN}$            | -                     | _                     | 50     | ns       | 1)                                                                                                                       |  |

| Data O   | utput Timing. See Figure 14 and Fig          | jure 15              |                       | "                     | "      |          |                                                                                                                          |  |

| 4.4.61   | SDO Rise Time                                | $t_{rSDO}$           | _                     | 10                    | 25     | ns       | $C_{load} = 40pF^{-1}$                                                                                                   |  |

| 4.4.62   | SDO Fall Time                                | $t_{fSDO}$           | _                     | 10                    | 25     | ns       | $C_{load} = 40pF^{-1}$                                                                                                   |  |

| 4.4.63   | SDO Valid Time                               | $t_{\sf VASDO}$      | _                     | 20                    | 50     | ns       | $V_{\rm SDO} < 0.2 V_{\rm DD} \ V_{\rm SDO} > 0.7 V_{\rm DD} \ {\rm C_{load}} = 40 {\rm pF}^{-1}$                        |  |

| 4.4.64   | SDO Enable Time after CSN falling edge       | $t_{\sf ENSDO}$      | -                     | -                     | 50     | ns       | Low Impedance 1)                                                                                                         |  |

| 4.4.65   | SDO Disable Time after CSN rising edge       | $t_{\sf DISSDO}$     | -                     | -                     | 50     | ns       | High Impedance 1)                                                                                                        |  |

| 4.4.66   | Duty cycle of incoming clock at SCLK         | duty <sub>SCLK</sub> | 40                    | -                     | 60     | %        | 1)                                                                                                                       |  |

### Electrical Characteristics (cont'd)

$V_{\rm S}$ = 7 V to 18 V,  $V_{\rm DD}$ = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40 °C to +150 °C, INH = HIGH;  $I_{\rm OUT1-10}$  = 0 A; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                         | Symbol                   | L    | imit Val | ues  | Unit     | Conditions      |

|--------|---------------------------------------------------|--------------------------|------|----------|------|----------|-----------------|

|        |                                                   |                          | Min. | Тур.     | Max. |          |                 |

| Therma | al Prewarning & Shutdown                          |                          |      |          |      | <u>'</u> |                 |

| 4.4.67 | Thermal warning junction temperature              | $T_{jW\_enter}$          | 120  | 140      | 170  | °C       | See Figure 6 1) |

| 4.4.68 | Thermal warning junction temperature - switch off | $T_{jW\_exit}$           | 90   | _        | 140  | °C       |                 |

| 4.4.69 | Temperature warning hysteresis                    | $\Delta T_{iW}$          | _    | 30       | _    | K        |                 |

| 4.4.70 | Thermal shutdown junction temperature             | $T_{jSD}$                | 150  | 175      | 200  | °C       |                 |

| 4.4.71 | Thermal switch-on junction temperature            | $T_{jSO}$                | 130  | _        | 180  | °C       |                 |

| 4.4.72 | Temperature shutdown hysteresis                   | $\Delta T_{jSD}$         | _    | 20       | _    | K        |                 |

| 4.4.73 | Ratio of SD to W temperature                      | $T_{\rm iSD}/T_{\rm iW}$ | 1.05 | 1.20     | _    | _        |                 |

<sup>1)</sup> Not subject to production test, specified by design

Data Sheet 14 Rev. 1.0, 2010-04-27

<sup>2)</sup> CSN High Time: This is the minimum time the user must wait between SPI commands

# 5 Block Description

#### 5.1 General

### 5.2 Power Supply

#### 5.2.1 General

The TLE84110EL has two power supply inputs: The half bridge outputs are connected to  $V_{\rm S}$  supply, which is connected to the 12V automotive supply rail. The internal logic part is supplied by a separate voltage  $V_{\rm DD}$  = 5 V.  $V_{\rm S}$  and  $V_{\rm DD}$  supplies are separated so that information stored in the logic block remains intact in the event of voltage drop outs or disturbances on  $V_{\rm S}$ . The system can therefore continue to operate once  $V_{\rm S}$  has recovered, without having to resend commands to the device.

A rising edge on  $V_{\rm DD}$  triggers an internal Power-On Reset (POR) to initialize the IC at power-on. All data stored internally is deleted, and the outputs are switched to high-impedance status (tristate). A 10 $\mu$ F electrolytic and 100nF ceramic capacitor are recommended to be placed as close as possible to the  $V_{\rm S}$  supply pin of the device for improved EMC performance in the high and low frequency band.

#### 5.2.2 Sleep Mode

The TLE84110EL enters low power mode (or sleep mode) by setting the INH input to low. The INH input has an internal pull-down resistor. In sleep-mode, all output transistors are turned off and the SPI register banks are reset.

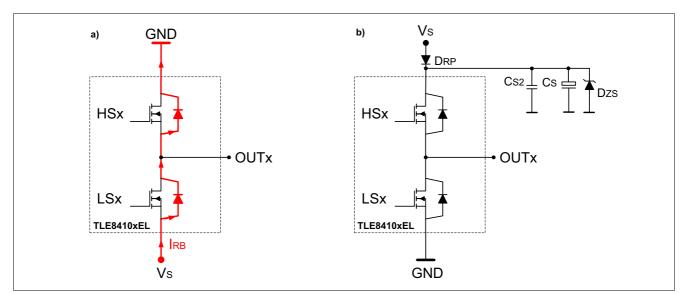

# 5.2.3 Reverse Polarity Protection

The TLE84110EL requires an external reverse polarity protection. During reverse polarity, the freewheeling diodes across the half bridge output will begin to conduct, causing an undesired current flow ( $I_{RB}$ ) from ground potential to battery and excessive power dissipation across the diodes. As such, a reverse polarity protection diode is recommended (see **Figure 4**).

Figure 4 Reverse Polarity Protection

#### 5.2.4 Power Supply Monitoring

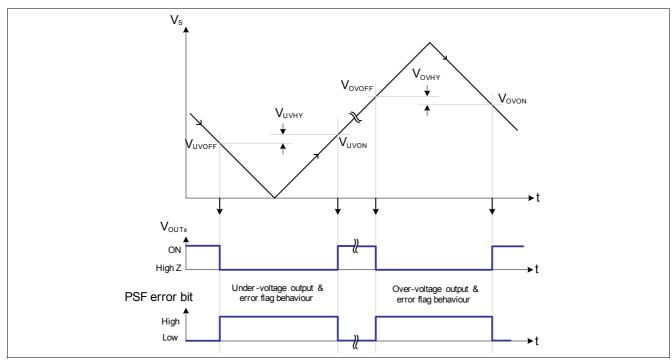

The power supply rails  $V_{\rm S}$  and  $V_{\rm DD}$  are monitored for over- and undervoltage. See **Figure 5**.

Data Sheet 15 Rev. 1.0, 2010-04-27

### 5.2.4.1 $V_{\rm S}$ Undervoltage

If the supply voltage  $V_{\rm S}$  drops below the switch off voltage  $V_{\rm UVOFF}$ , all output transistors are switched off but logic information remains intact and uncorrupted. The "undervoltage" (Power Supply Fail, PSF) error bit is flagged and can be read out via SPI. Once  $V_{\rm S}$  rises again and reaches the threshold switch on voltage  $V_{\rm UVON}$ , the power stages are restarted and the PSF error bit is reset.

# 5.2.4.2 $V_{\rm S}$ Overvoltage

If the supply voltage  $V_{\rm S}$  rises above the switch off voltage  $V_{\rm OVOFF}$ , all output transistors are switched off and the "overvoltage" (PSF) error bit is set. The error is not latched, i.e. if  $V_{\rm S}$  falls again and reaches the switch on voltage  $V_{\rm OVON}$ , the power stages are restarted and the Error Flags are reset.

Figure 5 Output behavior during Over- and Undervoltage V<sub>S</sub> condition

# 5.2.5 Reset Behavior

The following reset triggers have been implemented in the TLE84110EL:-

#### $V_{\rm DD}$ Undervoltage Reset:

The SPI Interface shall not function if  $V_{\rm DD}$  is below the undervoltage threshold,  $V_{\rm DD\,POffR}$ . The digital Block will be initialized. The output stages are switched off to High-Z. The undervoltage reset and SRR is released once  $V_{\rm DD}$  voltage levels are above the undervoltage threshold,  $V_{\rm DD\,POR}$ .

#### Reset on INH pin:

If the INH pin level is low, the device shall enter reset and the current consumption is reduced to  $I_{SQ} + I_{DD\_Q}$ .

Data Sheet 16 Rev. 1.0, 2010-04-27

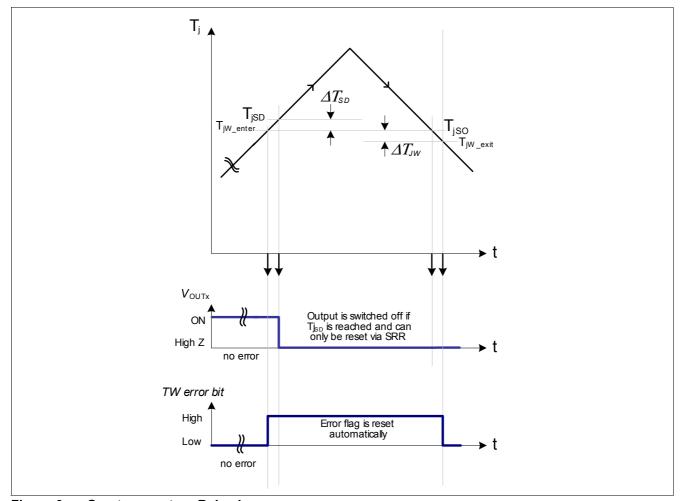

# 5.3 Temperature Monitoring

Temperature sensors are integrated in the power stages. The temperature monitoring circuit compares the measured temperature to the warning and shutdown thresholds. If one or more temperature sensors reach the warning temperature, the temperature warning bit, TW is set to HIGH. This bit is not latched (i.e. if the temperature falls below the warning threshold (with hysteresis), the TW bit is reset to LOW again).

If one or more temperature sensors reach the shut-down temperature threshold, all outputs are shut down and latched (i.e. the output stages remain off until an SRR command is sent or a power-on reset is performed). See **Figure 6**.

Figure 6 Overtemperature Behavior

Data Sheet 17 Rev. 1.0, 2010-04-27

#### 5.4 Protection and Diagnosis

This device features embedded protective functions which are designed to prevent IC destruction under fault conditions described in the following sections. Fault conditions are treated as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

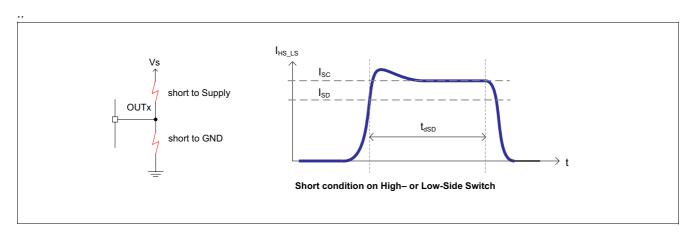

# 5.4.1 Short Circuit of Output to Supply or Ground

The high-side switches are protected against short to ground where as the low-side switches are protected against short to supply.

If a switch is turned on and the current rises above the overcurrent shutdown threshold,  $I_{\rm SD}$  for longer than the shutdown delay time  $t_{\rm dSD}$ , the output transistor is turned off and the corresponding diagnosis bit, OC, is set. During this delay time, the current is limited to  $I_{\rm SC}$  as shown in **Figure 7**. The output stage remains off and the error bit remains set until a status register reset is sent to the SPI or a power-on reset is performed.

Figure 7 High-Side and Low-Side Switch - Short Circuit and Overcurrent Protection

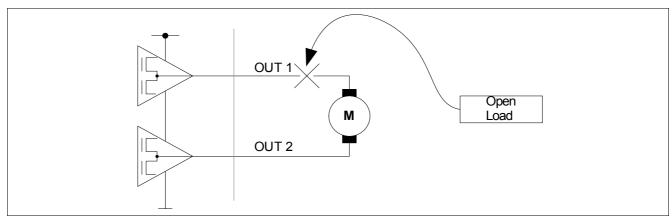

#### 5.4.2 Open Load

Open-load detection in ON-state is implemented in the Low-Side switches of the bridge outputs: If the current through the low side transistor is lower than the reference current  $I_{\rm OLD}$  in ON-state for longer than the open-load detection delay time  $t_{\rm dOLD}$ , the corresponding open-load, OL diagnosis bit is set. The output transistor, however, remains ON. The open load error bit is latched and can be reset by the SPI status register reset or by a power-on reset.

As an example, if a motor is connected between outputs OUT 1 and OUT 2 with a broken wire as shown in Figure 8, the resulting diagnostic information is shown in Table 2.

Open Load Detection Shutdown (OL SD EN) Bit via the Control Register can be activated or deactivated as required. If the OL SD EN bit is set and an open load on the Low-Side Switch is detected, the respective output is disabled. The error remains latched and output is off until an SRR or power on reset is performed. This has the added advantage of independently diagnosing and isolating error flags to the corresponding failed output.

Data Sheet 18 Rev. 1.0, 2010-04-27

Figure 8 Open Load Example

Table 2 Open Load Diagnosis Example

| Control   |           |               |           |                    | Diagnostic Information |                                       |            |            |              |  |  |  |

|-----------|-----------|---------------|-----------|--------------------|------------------------|---------------------------------------|------------|------------|--------------|--|--|--|

|           |           | Motor<br>Conn |           |                    |                        | Open Load Detection (OPLD) Error Flag |            |            |              |  |  |  |

| LS1<br>ON | HS1<br>ON | LS2<br>ON     | HS2<br>ON | Motor Rotation     | LS1<br>OpL             | LS2<br>OpL                            | LS1<br>OpL | LS2<br>OpL |              |  |  |  |

| 0         | 0         | 0             | 0         | motor off          | 0                      | 0                                     | 0          | 0          | de-activated |  |  |  |

| 1         | 0         | 0             | 1         | clock-wise         | 0                      | 0                                     | 1          | 0          | activated    |  |  |  |

| 0         | 1         | 1             | 0         | counter clock-wise | 0                      | 0                                     | 0          | 1          | activated    |  |  |  |

| 0         | 1         | 0             | 1         | brake high         | 0                      | 0                                     | 0          | 0          | de-activated |  |  |  |

| 1         | 0         | 1             | 0         | brake low          | 1                      | 1                                     | 1          | 1          | activated    |  |  |  |

#### 5.4.3 Cross-Current

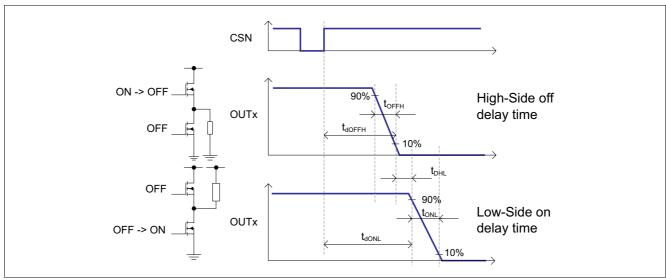

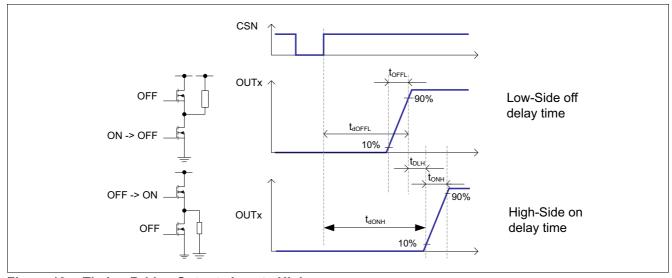

In bridge configurations the high-side and low-side power transistors are ensured never to be simultaneously "ON" to avoid cross currents. This is realized by integrating delays in the driver stage of the power outputs, intended to create a dead-time between switching off one Power Transistor and switching on of the other Power Transistor of the same half-bridge. To ensure that there is no overlap of the switching slopes that would lead to a cross current, the dead-times,  $t_{\rm DHL}$  and  $t_{\rm DLH}$  are specified.

In the event a cross-current has occurred, the device shall turn off both switches and the Overcurrent bit is set High.

Figure 9 Timing Bridge Outputs High to Low

Figure 10 Timing Bridge Outputs Low to High

#### 6.1 General

Infineon

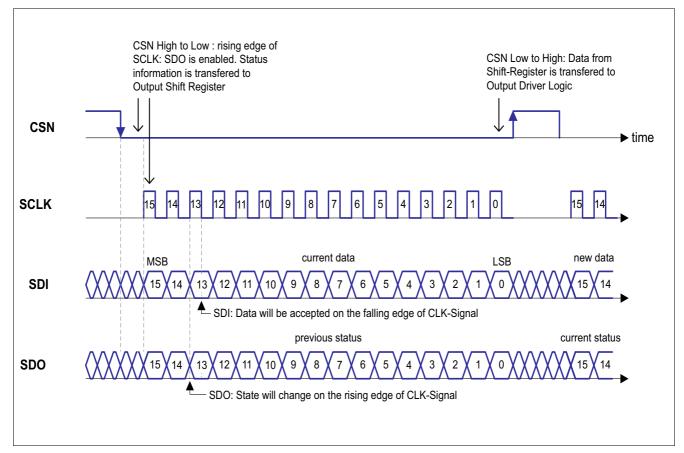

The SPI is used for bidirectional communication with a control unit. The TLE84110EL acts as SPI-slave and the control unit acts as SPI-master. The 16-bit control word is read via the SDI serial data input. The status word appears synchronously at the SDO serial data output. The communication is synchronized by the serial clock input SCLK.

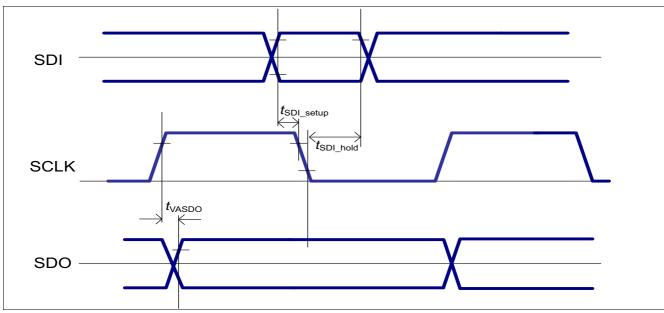

Standard data transfer timing is shown in **Figure 11**. The clock polarity is data valid on falling edge. SCLK must be low during CSN transition. The transfer is MSB first.

The transmission cycle begins when the chip is selected with the chip-select-not (CSN) input (H to L). Then the data is clocked through the shift register. The transmission ends when the CSN input changes from L to H and the word which has been read into the shift register becomes the control word. The SDO output switches then to tristate status, thereby releasing the SDO bus circuit for other uses. The SPI allows to parallel multiple SPI devices by using multiple CSN lines. The SPI can also be used with other SPI-devices in a daisy-chain configuration.

The control word transmitted from the master to the TLE84110EL is executed at the end of the SPI transmission (  $CSN\ L\ ->\ H\ )$  and remains valid until a different control word is transmitted or a power on reset occurs. At the beginning of the SPI transmission (  $CSN\ H\ ->\ L\ )$ , the diagnostic data currently valid are latched into the SPI and transferred to the master.

Data integrity is maintained by polling multiples of 8 data bits to ensure that a valid command has been received.

Figure 11 SPI Data Transfer Protocol

Data Sheet 21 Rev. 1.0, 2010-04-27

Figure 12 SPI SCLK and CSN

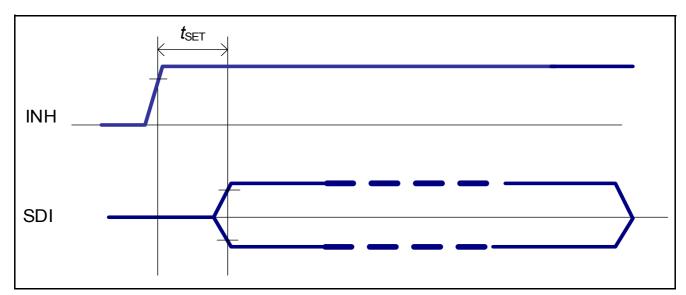

Figure 13 INH and SDI

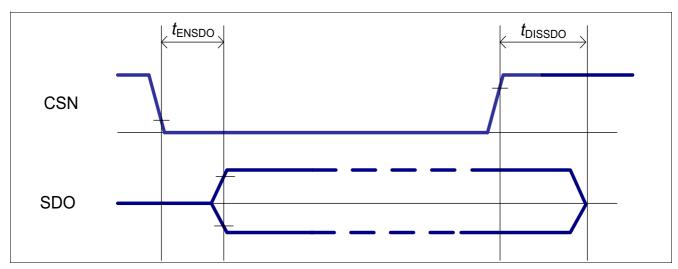

Figure 14 SPI SDO and CSN

Figure 15 SPI SDI, SDO and SCLK

### 6.2 Status Register Reset

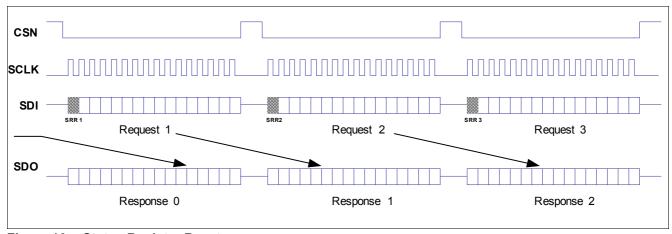

The SPI is using a standard shift-register concept with daisy-chain capability. Any data transmitted to the SPI will be available to the internal logic part at the end of the SPI transmission (CSN L -> H). To read a specific register, the address of the register is sent by the master to the SPI in a first SPI frame. The data that corresponds to this address is transmitted by the SDO during the following (second) SPI frame to the master. The default address for Status Register transmission after Power-ON Reset is 0.

The Status-Register-Reset command-bit is executed after the next SPI transmission. The two bits, Address Register and SRR act as command to read and reset (or not reset) the addressed Status-Register. The request and response behaviour of the SPI is further illustrated in **Figure 16** below.

Figure 16 Status Register Reset

# 6.3 SPI Bit Definitions

# 6.3.1 Control - Word

# **Control Register Overview**

### Control Register 0 for HB 1: HB 6

| 15  | 14 | 13           | 12          | 11          | 10          | 9           | 8           | 7           | 6            | 5            | 4            | 3            | 2            | 1            | 0 |

|-----|----|--------------|-------------|-------------|-------------|-------------|-------------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|---|

| SRR | 0  | OL_SD<br>_EN | ACT_<br>HB6 | ACT_<br>HB5 | ACT_<br>HB4 | ACT_<br>HB3 | ACT_<br>HB2 | ACT_<br>HB1 | CONF_<br>HB6 | CONF_<br>HB5 | CONF_<br>HB4 | CONF_<br>HB3 | CONF_<br>HB2 | CONF_<br>HB1 | 0 |

# Control Register 1 for HB 7 : HB 10

| 15  | 14 | 13           | 12 | 11 | 10           | 9           | 8           | 7           | 6 | 5 | 4             | 3            | 2            | 1            | 0 |

|-----|----|--------------|----|----|--------------|-------------|-------------|-------------|---|---|---------------|--------------|--------------|--------------|---|

| SRR | 1  | OL_SD<br>_EN | x  | x  | ACT_<br>HB10 | ACT_<br>HB9 | ACT_<br>HB8 | ACT_<br>HB7 | x | x | CONF_<br>HB10 | CONF_<br>HB9 | CONF_<br>HB8 | CONF_<br>HB7 | 0 |

### Table 3 Input (Control) Data Register

| Bit    | Control<br>Register - 0<br>HB 1:6 | Control<br>Register - 1<br>HB 7:10 | Control Register - 0<br>HB 1:6<br>DESCRIPTION                                                                                                                                                                                                                  | Control Register - 1 HB 7:10 DESCRIPTION                                                                                                                                                                                                      |

|--------|-----------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Diagr  | nosis & Regist                    | er Control                         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                               |

| 15     | SRR<br>(HB1:6)                    | SRR<br>(HB7:10)                    | Status Register Reset (SRR) for HB1 to HB 6. If set to high, the errors bits of the coresponding status register are reset on the rising edge of CSN if sent to the uC. Low indicates no reset.                                                                | Status Register Reset (SRR) for HB7 to HB 10. If set to high, the errors bits of the coresponding status register are reset on the rising edge of CSN if sent to the uC. Low indicates no reset.                                              |

| 14     | 0                                 | 1                                  | Address Register                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                               |

| 13     | OL SD EN<br>(HB1:6)               | OL SD EN<br>(HB7:10)               | Open Load Detection Shutdown<br>Enable (OL SD EN) for HB1 to HB 6.<br>This feature allows the affected<br>output stage to be switched off if a<br>true open load or underload<br>condition has been detected. It can<br>be activated or deactivated by bit 13. | Open Load Detection Shutdown Enable (OL SD EN) for HB7 to HB 10. This feature allows the affected output stage to be switched off if a true open load or underload condition has been detected. It can be activated or deactivated by bit 13. |

| Activa | te Half-Bridge                    | X                                  |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                               |

| 12     | ACT_HB 6                          | X                                  | H => Half Bridge 6 is active<br>L => Half Bridge 6 is in Hi-Z                                                                                                                                                                                                  | X => Don't Care                                                                                                                                                                                                                               |

| 11     | ACT_HB 5                          | X                                  | H => Half Bridge 5 is active<br>L => Half Bridge 5 is in Hi-Z                                                                                                                                                                                                  | X => Don't Care                                                                                                                                                                                                                               |

| 10     | ACT_HB 4                          | ACT_HB 10                          | H => Half Bridge 4 is active<br>L => Half Bridge 4 is in Hi-Z                                                                                                                                                                                                  | H => Half Bridge 10 is active<br>L => Half Bridge 10 is in Hi-Z                                                                                                                                                                               |

Data Sheet 24 Rev. 1.0, 2010-04-27

Table 3 Input (Control) Data Register

| Bit   | Control<br>Register - 0<br>HB 1:6 | Control<br>Register - 1<br>HB 7:10 | Control Register - 0 HB 1:6 DESCRIPTION                       | Control Register - 1 HB 7:10 DESCRIPTION                       |

|-------|-----------------------------------|------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------|

| 9     | ACT_HB 3                          | ACT_HB 9                           | H => Half Bridge 3 is active<br>L => Half Bridge 3 is in Hi-Z | H => Half Bridge 9 is active<br>L => Half Bridge 9 is in Hi-Z  |

| 8     | ACT_HB 2                          | ACT_HB 8                           | H => Half Bridge 2 is active<br>L => Half Bridge 2 is in Hi-Z | H => Half Bridge 8 is active<br>L => Half Bridge 8 is in Hi-Z  |

| 7     | ACT_HB 1                          | ACT_HB 7                           | H => Half Bridge 1 is active<br>L => Half Bridge 1 is in Hi-Z | H => Half Bridge 7 is active<br>L => Half Bridge 7 is in Hi-Z  |

| Confi | gure Half-Brid                    | ge X                               |                                                               |                                                                |

| 6     | CONF_HB 6                         | X                                  | H => HSD6 = ON & LSD6 = OFF<br>L => HSD6 = OFF & LSD6 = ON    | X => Don't Care                                                |

| 5     | CONF_HB 5                         | Х                                  | H => HSD5 = ON & LSD5 = OFF<br>L => HSD5 = OFF & LSD5 = ON    | X => Don't Care                                                |

| 4     | CONF_HB 4                         | CONF_HB 10                         | H => HSD4 = ON & LSD4 = OFF<br>L => HSD4 = OFF & LSD4 = ON    | H => HSD10 = ON & LSD10 = OFF<br>L => HSD10 = OFF & LSD10 = ON |

| 3     | CONF_HB 3                         | CONF_HB 9                          | H => HSD3 = ON & LSD3 = OFF<br>L => HSD3 = OFF & LSD3 = ON    | H => HSD9 = ON & LSD9 = OFF<br>L => HSD9 = OFF & LSD9 = ON     |

| 2     | CONF_HB 2                         | CONF_HB 8                          | H => HSD2 = ON & LSD2 = OFF<br>L => HSD2 = OFF & LSD2 = ON    | H => HSD8 = ON & LSD8 = OFF<br>L => HSD8 = OFF & LSD8 = ON     |

| 1     | CONF_HB 1                         | CONF_HB 7                          | H => HSD1 = ON & LSD1 = OFF<br>L => HSD1 = OFF & LSD1 = ON    | H => HSD7 = ON & LSD7 = OFF<br>L => HSD7 = OFF & LSD7 = ON     |

| 0     | 0                                 |                                    | Least Significant Bit (LSB) is set                            | to Low                                                         |

# 6.3.2 Diagnosis - Word

### **Diagnosis Register Overview**

### Diagnosis Register 0 for HB 1: HB 6

| 15 | 14  | 13 | 12           | 11           | 10           | 9            | 8            | 7            | 6             | 5             | 4             | 3             | 2             | 1             | 0  |

|----|-----|----|--------------|--------------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|---------------|---------------|---------------|----|

| ос | PSF | OL | SACT_<br>HB6 | SACT_<br>HB5 | SACT_<br>HB4 | SACT_<br>HB3 | SACT_<br>HB2 | SACT_<br>HB1 | SCONF<br>_HB6 | SCONF<br>_HB5 | SCONF<br>_HB4 | SCONF<br>_HB3 | SCONF<br>_HB2 | SCONF<br>_HB1 | TW |

# Diagnosis Register 1 for HB 7 : HB 10

| 15 | 14  | 13 | 12 | 11 | 10            | 9            | 8            | 7            | 6 | 5 | 4              | 3 | 2             | 1             | 0  |  |

|----|-----|----|----|----|---------------|--------------|--------------|--------------|---|---|----------------|---|---------------|---------------|----|--|

| ос | PSF | OL | x  | x  | SACT_<br>HB10 | SACT_<br>HB9 | SACT_<br>HB8 | SACT_<br>HB7 | x | x | SCONF<br>_HB10 |   | SCONF<br>_HB8 | SCONF<br>_HB7 | TW |  |

### Table 4 Output (Status) Data Register

| Bit   | Status          | Status       | Status Register- 0                       | Status Register - 1                    |  |  |  |

|-------|-----------------|--------------|------------------------------------------|----------------------------------------|--|--|--|

|       | Register - 0    | Register - 1 | HB 1:6                                   | HB 7:10                                |  |  |  |

|       | HB 1:6          | HB 7:10      | DESCRIPTION                              | DESCRIPTION                            |  |  |  |

| Diag  | nosis & Regist  | er Control   |                                          |                                        |  |  |  |

| 15    | OC              | ОС           | Overcurrent Error is set if any one of   | Overcurrent Error is set if any one of |  |  |  |

|       | (HB1:6)         | (HB7:10)     | HB1 to HB6 has an overload, short        | HB7 to HB10 has an overload, short     |  |  |  |

|       |                 |              | circuit or cross current; The error is   | circuit or cross current; The error is |  |  |  |

|       |                 |              | latched and the corresponding output     | latched and the corresponding          |  |  |  |

|       |                 |              | is switched off;                         | output is switched off;                |  |  |  |

|       |                 |              | Bit 15 error can only be reset via SRR   | Bit 15 error can only be reset via     |  |  |  |

|       |                 |              | or power-on reset.                       | SRR or power-on reset.                 |  |  |  |

| 14    | PSF             |              | Power Supply Failure; Global Error       | Flag;                                  |  |  |  |

|       |                 |              | Bit 14 is set if VS has an overvoltag    | e or undervoltage condition;           |  |  |  |

|       |                 |              | All outputs are switched OFF.            |                                        |  |  |  |

|       |                 |              | Bit 14 is automatically reset if VS re   | turns to its normal operating range.   |  |  |  |

| 13    | OL OL           |              | Open Load Error is set if any one of     | Open Load Error is set if any one of   |  |  |  |

|       | (HB1:6)         | (HB7:10)     | HB1 to HB6 has a true open load or       | HB7 to HB10 has a true open load or    |  |  |  |

|       |                 |              | underload error condition; The error     | underload error condition; The error   |  |  |  |

|       |                 |              | is latched. The corresponding output     | is latched. The corresponding output   |  |  |  |

|       |                 |              | is switched off if Bit 13, OL SD EN of   | is switched off if Bit 13, OL SD EN of |  |  |  |

|       |                 |              | the Control Register is activated or     | the Control Register is activated or   |  |  |  |

|       |                 |              | high. Bit 13 error can only be reset via | high. Bit 13 error can only be reset   |  |  |  |

|       |                 |              | SRR or power-on reset.                   | via SRR or power-on reset.             |  |  |  |

| Activ | ate Half-Bridge | X            |                                          |                                        |  |  |  |

| 12    | SACT_HB 6       | X            | H => Half Bridge 6 is active             | X => Don't Care                        |  |  |  |

|       |                 |              | L => Half Bridge 6 is in Hi-Z            |                                        |  |  |  |

| 11    | SACT_HB 5       | X            | H => Half Bridge 5 is active             | X => Don't Care                        |  |  |  |

|       | _               |              | L => Half Bridge 5 is in Hi-Z            |                                        |  |  |  |

|       |                 |              | 2 Trail Bridge 6 15 III Til 2            |                                        |  |  |  |

Table 4 Output (Status) Data Register

| Bit  | Status<br>Register - 0<br>HB 1:6 | Status<br>Register - 1<br>HB 7:10 | Status Register- 0<br>HB 1:6<br>DESCRIPTION                   | Status Register - 1<br>HB 7:10<br>DESCRIPTION                                                                          |

|------|----------------------------------|-----------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 10   | SACT_HB 4                        | SACT_HB 10                        | H => Half Bridge 4 is active<br>L => Half Bridge 4 is in Hi-Z | H => Half Bridge 10 is active<br>L => Half Bridge 10 is in Hi-Z                                                        |

| 9    | SACT_HB 3                        | SACT_HB 9                         | H => Half Bridge 3 is active<br>L => Half Bridge 3 is in Hi-Z | H => Half Bridge 9 is active<br>L => Half Bridge 9 is in Hi-Z                                                          |

| 8    | SACT_HB 2                        | SACT_HB 8                         | H => Half Bridge 2 is active<br>L => Half Bridge 2 is in Hi-Z | H => Half Bridge 8 is active<br>L => Half Bridge 8 is in Hi-Z                                                          |

| 7    | SACT_HB 1                        | SACT_HB 7                         | H => Half Bridge 1 is active<br>L => Half Bridge 1 is in Hi-Z | H => Half Bridge 7 is active<br>L => Half Bridge 7 is in Hi-Z                                                          |

| Conf | igure Half-Bridç                 | ge X                              |                                                               |                                                                                                                        |

| 6    | SCONF_HB<br>6                    | X                                 | H => HSD6 = ON & LSD6 = OFF<br>L => HSD6 = OFF & LSD6 = ON    | X => Don't Care                                                                                                        |

| 5    | SCONF_HB<br>5                    | Х                                 | H => HSD5 = ON & LSD5 = OFF<br>L => HSD5 = OFF & LSD5 = ON    | X => Don't Care                                                                                                        |

| 4    | SCONF_HB<br>4                    | SCONF_HB<br>10                    | H => HSD4 = ON & LSD4 = OFF<br>L => HSD4 = OFF & LSD4 = ON    | H => HSD10 = ON & LSD10 = OFF<br>L => HSD10 = OFF & LSD10 = ON                                                         |

| 3    | SCONF_HB                         | SCONF_HB<br>9                     | H => HSD3 = ON & LSD3 = OFF<br>L => HSD3 = OFF & LSD3 = ON    | H => HSD9 = ON & LSD9 = OFF<br>L => HSD9 = OFF & LSD9 = ON                                                             |

| 2    | SCONF_HB<br>2                    | SCONF_HB<br>8                     | H => HSD2 = ON & LSD2 = OFF<br>L => HSD2 = OFF & LSD2 = ON    | H => HSD8 = ON & LSD8 = OFF<br>L => HSD8 = OFF & LSD8 = ON                                                             |

| 1    | SCONF_HB<br>1                    | SCONF_HB<br>7                     | H => HSD1 = ON & LSD1 = OFF<br>L => HSD1 = OFF & LSD1 = ON    | H => HSD7 = ON & LSD7 = OFF<br>L => HSD7 = OFF & LSD7 = ON                                                             |